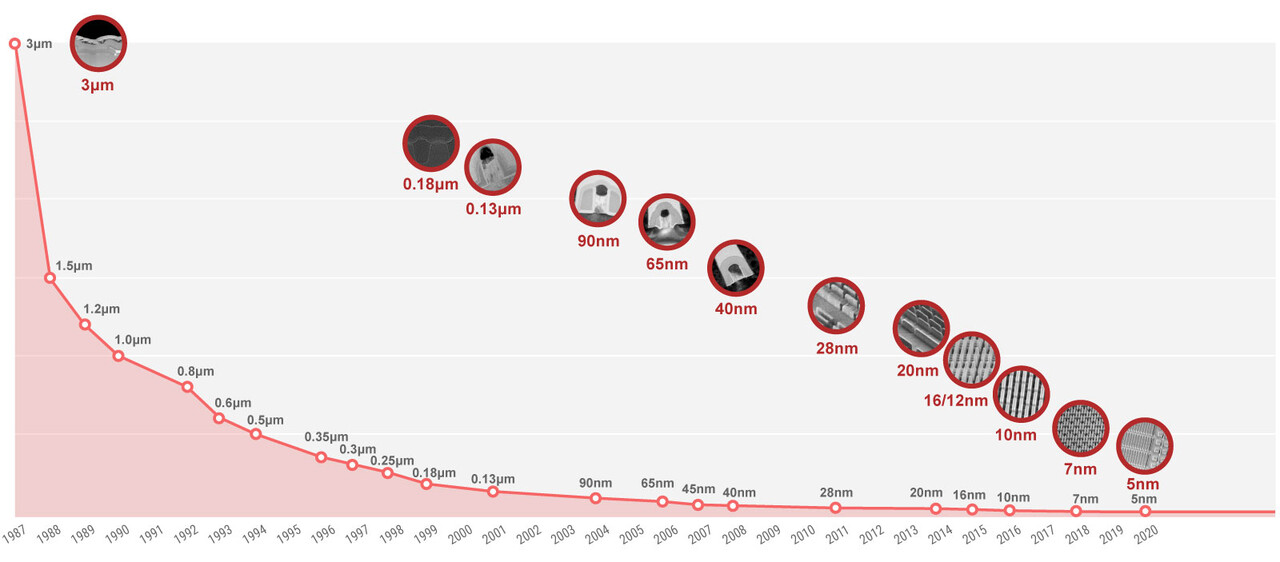

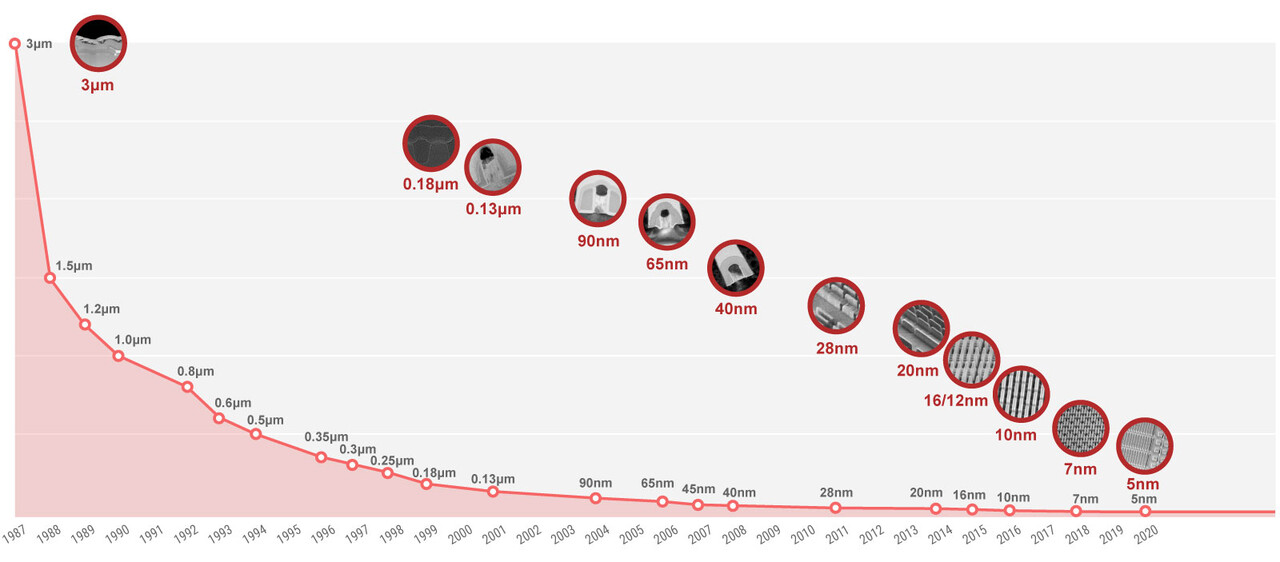

Kế hoạch sản xuất trên node N3E vào Q3/2023 của TSMC có thể sẽ diễn ra sớm hơn nhờ năng suất trên node này tốt hơn dự kiến. Theo báo cáo từ ngân hàng Morgan Stanley, TSMC có thể sẽ đóng băng quy trình N3E sớm vào khoảng cuối tháng 3 năm nay và đi vào sản xuất từ Q2/2023, sớm hơn 1 quý so với kế hoạch ban đầu.

Hiện tại TSMC đang phát triển nhiều node N3, gồm N3, N3B và N3E. Ban đầu N3E được coi là phiên bản nâng cao hơn của N3, tuy nhiên giờ đây nó lại giống phiên bản thay thế hơn. Năng suất sản xuất thử nghiệm của N3E cao hơn nhiều so với N3B, mật độ logic của N3E chỉ kém 8% so với N3 ban đầu sau khi cắt bớt 4 lớp quang khắc cực tím (EUV - extreme ultraviolet lithography), từ 25 lớp còn 21 lớp, do đó sản xuất dễ dàng hơn. Nếu so với N5, N3E có mật độ logic dày đặc hơn 60%, trong khi N3 được cho là có mật độ logic dày hơn 70%. Điều này làm cho N3E trở thành node mang tính cạnh tranh tốt hơn về mặt chi phí cũng như thời gian.

Theo tiến sĩ C.C. Wei - CEO của TSMC - thì N3E node có cửa sổ quy trình sản xuất được cải thiện với hiệu suất, công suất và năng suất tốt hơn, do vậy đây nhiều khả năng là node được ứng dụng nhiều hơn cho các sản phẩm silicon hiệu suất cao trong tương lai. Thông tin của Morgan Stanley được đưa ra trong bối cảnh các nguồn tin trên báo chí Đài Loan phỏng đoán rằng TSMC đang gặp khó khăn với năng suất trên node 3 nm. Ngoài ra, node N3B cũng là 1 phiên bản cải tiến của N3, dành cho 1 số khách hàng nhất định, dù vậy hiện tại chưa có thông tin gì nhiều về N3B.

Link nguồn dưới comment.

Hiện tại TSMC đang phát triển nhiều node N3, gồm N3, N3B và N3E. Ban đầu N3E được coi là phiên bản nâng cao hơn của N3, tuy nhiên giờ đây nó lại giống phiên bản thay thế hơn. Năng suất sản xuất thử nghiệm của N3E cao hơn nhiều so với N3B, mật độ logic của N3E chỉ kém 8% so với N3 ban đầu sau khi cắt bớt 4 lớp quang khắc cực tím (EUV - extreme ultraviolet lithography), từ 25 lớp còn 21 lớp, do đó sản xuất dễ dàng hơn. Nếu so với N5, N3E có mật độ logic dày đặc hơn 60%, trong khi N3 được cho là có mật độ logic dày hơn 70%. Điều này làm cho N3E trở thành node mang tính cạnh tranh tốt hơn về mặt chi phí cũng như thời gian.

Theo tiến sĩ C.C. Wei - CEO của TSMC - thì N3E node có cửa sổ quy trình sản xuất được cải thiện với hiệu suất, công suất và năng suất tốt hơn, do vậy đây nhiều khả năng là node được ứng dụng nhiều hơn cho các sản phẩm silicon hiệu suất cao trong tương lai. Thông tin của Morgan Stanley được đưa ra trong bối cảnh các nguồn tin trên báo chí Đài Loan phỏng đoán rằng TSMC đang gặp khó khăn với năng suất trên node 3 nm. Ngoài ra, node N3B cũng là 1 phiên bản cải tiến của N3, dành cho 1 số khách hàng nhất định, dù vậy hiện tại chưa có thông tin gì nhiều về N3B.

Link nguồn dưới comment.